2. Da AHCI a NVMe

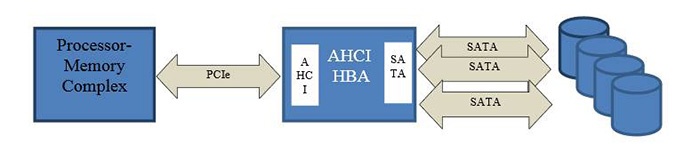

L'Advanced Host Controller Interface (AHCI) viene utilizzata come elemento logico in grado di mettere in comunicazione due bus fisici aventi caratteristiche strutturali differenti: da una parte l'interconnessione alla base delle periferiche host di tipo PCI/PCIe e, dall'altra, il sottosistema di storage appoggiato all'interfaccia di dispositivo SATA.

L'AHCI, impiegata nell'ambito di utilizzo degli Host Bus Adapter (HBA), ha in pratica la funzione di interfaccia tra i suddetti bus al fine di mitigare le sensibili differenze di larghezza di banda e di latenza, caratteristiche peculiari di questo tipo di interconnessioni.

Le latenze introdotte dall'HBA, dovute per lo più ad una serie di inefficienze operative causate da compromessi architetturali, sono rimaste pressoché ininfluenti nei sistemi facenti uso dei classici sistemi di storage a tipologia magnetica (HDD): in tali sistemi, infatti, è possibile raggiungere prestazioni complessive ancora oggi ben al di sotto del limite teorico.

Tali latenze sono invece venute ad assumere una valenza ben più consistente nel momento in cui sono stati adottati i moderni SSD, dispositivi in cui i tempi di accesso ai dati appaiono estremamente più ridotti.

In queste circostanze il throughput che ne deriva va ad attestarsi su livelli di gran lunga più elevati, in grado di spingersi anche oltre il limite prestazionale teorico del sottostante sistema di storage.

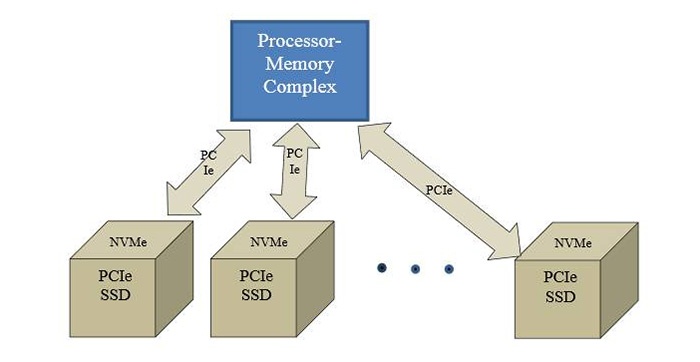

La chiara origine di queste limitazioni ha inevitabilmente, nell'ultimo periodo, portato lo sviluppo dei produttori del settore verso una definitiva transizione dalla vecchia idea di connessione basata sui bus tradizionali verso una più efficiente concezione di trasmissione dei dati su canali di comunicazione dislocati quanto più vicini alle unità di elaborazione dei dispositivi host.

In maniera quasi del tutto inevitabile, il consorzio dei produttori è giunto pertanto all'idea di utilizzare le unità di storage direttamente comunicanti attraverso le connessioni ultra-veloci offerte dal bus e dagli slot PCIe, in modo da offrire tutta una serie di canali di comunicazione, per quanto possibile, privi di cause di rallentamento.

Come naturale conseguenza di questo step tecnologico evolutivo, si è reso altresì necessario che la nuova tipologia di collegamento richiedesse anche la definizione di una altrettanto nuova interfaccia di interconnessione a livello logico.

E' proprio in questo ambito che va ad inserirsi l'insieme delle nuove regole del protocollo di comunicazione NVMe (Non-Volatile Memory Express).

Le principali caratteristiche funzionali di questa interfaccia sono state sviluppate, nel tentativo di evitare possibili futuri colli di bottiglia, alla luce di due fattori fondamentali a livello di comunicazione: la scalabilità e il parallelismo.

Questi sono, tra l'altro, dei benefici che hanno consentito l'adattamento immediato delle nuove regole all'interno di un'ampia varietà dei più moderni sistemi di elaborazione ed architetture, a partire dai laptop sino a giungere ai server più complessi.

La nuova modalità operativa, che sfrutta l'invio di dati fortemente parallelizzati, si integra alla perfezione con le caratteristiche elaborative delle CPU di ultima generazione (così come con quelle delle nuove piattaforme nonché delle applicazioni) garantendo da un lato prestazioni sinora inarrivabili e consentendo dall'altro una più efficiente gestione dell'enorme flusso dei dati veicolati, senza peraltro tutta quelle serie di limitazioni tipiche dei protocolli utilizzati in precedenza.

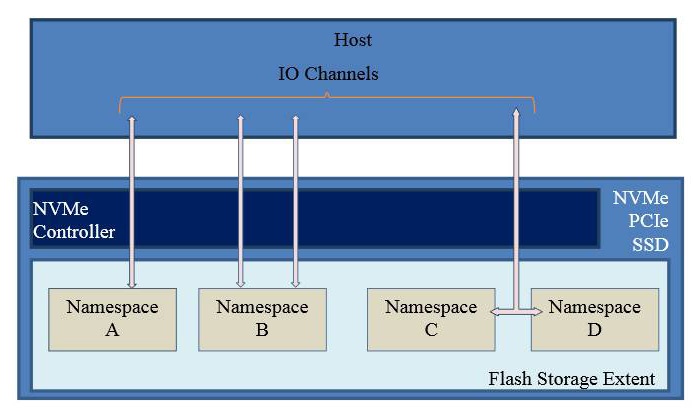

Altra importante caratteristica insita nell'interfaccia NVMe è il supporto al partizionamento dell'estensione fisica dello storage in estensioni logiche multiple: ad ognuna di queste ultime è data ora la possibilità di accesso in modalità totalmente indipendente da tutte le altre.

Ognuna di queste estensioni logiche, chiamate "spazio nome", può avere a disposizione un proprio canale di comunicazione indipendente (IO Channel), al quale l'host può accedere con estrema facilità , velocità e sicurezza.

Come si può notare dall'immagine soprastante, è del tutto intuitiva la creazione di canali multipli di comunicazione simultanea verso una singola cella "spazio nome", proprio in virtù del parallelismo che è alla base delle funzionalità della nuova interfaccia NVMe.

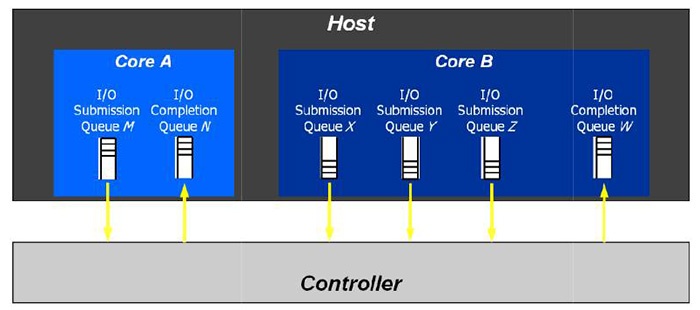

Oltre a quanto appena esposto, proprio per assicurare il massimo throughput al sottosistema di storage, le regole del protocollo NVMe permettono di utilizzare una svariata serie di code di comandi dedicati ad ogni core, processo o thread attivo sul sistema, eliminando del tutto la necessità della creazione di blocchi facenti uso del vecchio meccanismo "semaforico", causa principale della inefficienza sin qui rilevata.

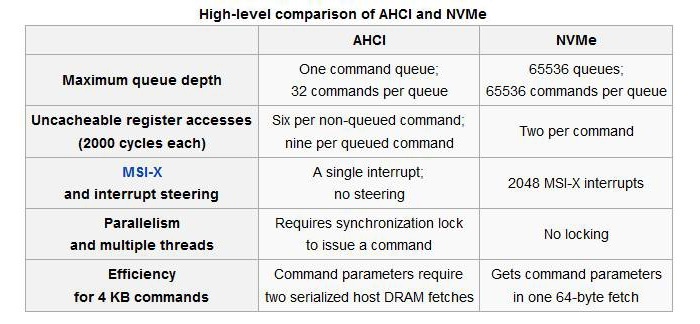

Vi proponiamo, infine, una tabella riportante le principali differenze funzionali tra le due interfacce logiche trattate in questa pagina.