2. Evoluzione delle SDRAM: dalle DDR3 alle DDR4 - Parte prima

In una logica indirizzata al processo evolutivo delle tecnologie informatiche, si inserisce di diritto l'esordio delle DDR4 nel mercato consumer.

Nonostante siano state progettate, fabbricate e collaudate già da qualche anno, soltanto a fine agosto hanno visto la prima implementazione sulle piattaforme desktop di fascia alta, equipaggiate con il nuovo chipset Intel X99.

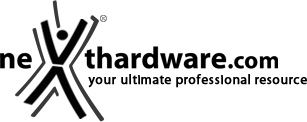

Il seguente schema ci mostra le differenze fisiche che intercorrono tra un modulo DDR4 ed i moduli DDR di precedenti generazioni.

Figura 1: Principali differenze fisiche tra diverse tipologie di moduli RAM

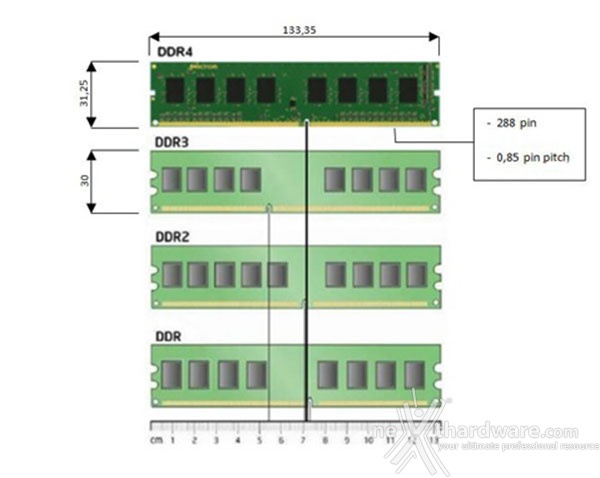

Figura 2: Quote PCB RAM DDR4

Le DDR (Double Data Rate) SDRAM sono tipicamente suddivise al proprio interno in una serie di banchi di memoria indipendenti: nelle DDR di terza generazione il numero di questi può essere 2, 4 o 8, mentre nel caso delle nuove DDR di quarta generazione i banchi possono arrivare sino a 16.

Tutte le memorie DDR consentono il prelevamento dei dati in modalità sincrona, con una temporizzazione che è due volte la frequenza del proprio clock di riferimento.

Pertanto, prendendo come metro di paragone il picco di trasferimento dei dati ottenuto da una vecchia DDR-400 (200Mhz, PC-3200) di prima generazione, una DIMM x64 di questo tipo di memoria presenta una velocità di trasferimento dei dati di 3200MB/s ovvero 3.2GB/s.

Questa performance è conseguita tramite l'utilizzo di un'architettura di tipo 2n-prefetch, dove il bus interno dei dati risulta ampio due volte il proprio bus esterno.

Il prelevamento dei dati avviene pertanto due volte per ciclo di clock, con le celle di memoria che trasferiscono i dati ai buffers di I/O a coppie, mentre la frequenza di accesso alla colonna interna si dimezza rispetto a quella del bus esterno.

Le memorie DDR rivelano, pertanto, un tipico esempio di progettazione source-synchronous, mentre, a titolo di paragone, nelle precedenti SDRAM di una ventina di anni fa, il progetto era di tipo fully-synchronous in quanto il prelevamento dei dati avveniva solo sul fronte positivo del clock: si trattava infatti di un'architettura di tipo 1n-prefetch.

Per ottenere l'integrità dei segnali ad alta velocità , le DDR SDRAM fanno uso di un data strobe bidirezionale, un'interfaccia SSTL_2 con input e clock differenziali, essendo pertanto in grado di gestire i segnali di un duplice clock, true (CK) e complementary (CK#).

Per selezionare il corretto banco interessato ai comandi, il memory controller utilizza la funzione Bank Address seguita dal relativo numero identificativo (BA0, BA1,BA2, ect.).

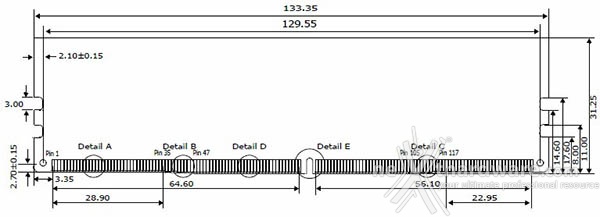

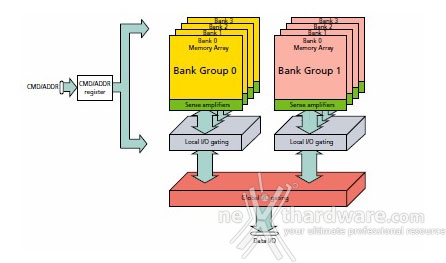

Nella fattispecie, le DDR4 supportano il raggruppamento dei banchi nelle seguenti configurazioni:

- Â x4/x8: quattro gruppi di banchi, ognuno formato da quattro ulteriori banchi (Fig.3);

- Â x16: due gruppi di banchi, ognuno formato da ulteriori quattro banchi (Fig.4).

Fig.3 Raggruppamento dei banchi - Config. X4 e X8

Fig.4 Raggruppamento dei banchi - Config. X16

Gli accessi a banchi appartenenti a gruppi differenti richiedono, nelle DDR4, minor tempo rispetto agli accessi tra due banchi dello stesso gruppo.

Infatti, nel caso in cui siano necessari accessi a banchi facenti parte di gruppo differenti, è possibile utilizzare timings più ridotti (tCCD_S, tRRD_S, tWTR_S), mentre nell'accesso a banchi appartenenti allo stesso gruppo si devono, per forza di cose, utilizzare temporizzazioni più prolungate (tCCD_L, tRRD_L, tWTR_L).

Per definirne alcune delle principali caratteristiche tecniche e cercare così di fare ulteriore chiarezza riguardo il funzionamento ed i vantaggi che derivano dall'adozione delle DDR4, riteniamo sia utile indicare alcune delle specifiche di targa, a livello di singolo IC, mettendole a confronto con quelle delle SDRAM di generazioni precedenti.

|  Product SDRAM | Clock Rate (tCK) | Data Rate  | Density | Prefetch (Burst Length) | Number of banks | ||

| Â Max | Min | Â Min | Â Max | ||||

| SDR | 10ns | 5ns | 100 MB/s | 200 MB/s | Â 64-512MB | Â 1n | 4 |

| DDR | 10ns | 5ns | 200 MB/s | 400 MB/s | Â 256MB-1GB | Â 2n | Â 4 |

| Â DDR2 | 5ns | 2.5ns | 400 MB/s | 800 MB/s | 512MB-2GB | Â 4n | Â 4,8 |

| DDR3 | 2.5ns | 1.25ns | 800 MB/s | 1600 MB/s | 512MB-8GB | Â 8n | 8 |

| DDR4 | 1.25ns | 0.625ns | 1600 MB/s | 3200 MB/s | 2-16GB | Â 8n | Â 8,16 |

L'aumento di densità introdotto nelle DDR4 (2-16GB) consente di avere la medesima capacità di memoria con un minor numero di ICs, a tutto vantaggio di una riduzione dei costi, oppure, al contrario, è possibile disporre di una maggiore quantità di memoria, pur mantenendo lo stesso numero di moduli installati.

Prefetch

Come si evince dalla tabella, da una generazione di DDR a quella successiva viene in genere ottenuto un raddoppio diretto del valore di Prefetch: ciò, invece, non avviene nel passaggio dalle DDR3 a DDR4, in cui il suddetto valore rimane invariato.

La spiegazione non è affatto complicata, in quanto un ipotetico raddoppio del Burst Length a 16, in abbinamento ad un modulo DDR4 contenente 8 blocchi indipendenti di memoria (Banks) in configurazione x16 porterebbe, ad ogni accesso, ad un trasferimento di dati pari a 32 bytes, recando innegabili benefici nel caso in cui si debbano trasferire blocchi di dati consistenti.

Purtroppo, non si avrebbe la stessa efficienza nel caso si avesse a che fare con blocchi di dati di piccole dimensioni: in tali circostanze il raddoppio del Burst Length porterebbe a risultati di sensibile inefficienza.

Le DDR4, come del resto le DDR3, fanno uso di una particolare modalità di Prefetch denominata Burst Chop 4 (BC4) la quale, per mezzo di un controllo interno dei segnali, seleziona (masked) soltanto i primi quattro bit di un Burst Length di 8 (BL=8,) in lettura o scrittura, portando anche l'intervallo di Column Command (tCCD) a divenire 4tCK nelle circostanze di 8-bit Prefetch.

Operando in tale modalità si hanno dei marginali benefici in termini di tempo impiegato nelle transizioni scrittura/lettura e lettura/scrittura che, tuttavia, tendono a vanificarsi quando vengono utilizzati pattern di accesso differenziati.

Ciò comporta, nelle peggiori delle circostanze, anche una perdita di efficienza nel caso si intendano trasferire files di grandi dimensioni con una elevata larghezza di banda.