Mentre in quel di Cupertino si discute ancora di HBM2, dettagliandone maggiormente caratteristiche e specifiche, con Samsung e SK Hynix che ne confermano l'arrivo sul mercato a fine anno (magari su AMD Vega per il mercato consumer), fanno già capolino le tecnologie che le andranno ad avvicendare, ovvero le HBM3 o Extreme HBM previste tra il 2019 ed il 2020.

| DRAM | GDDR5 | GDDR5X | HBM1 | HBM2 |

| I/O | 32 | 64 | 1024 | 1024 |

| Prefetch (per I/O) | 8 | 16 | 2 | 2 |

| Max. Bandwidth | 32GB/s (8Gbps per pin) | 64GB/s (12Gbps per pin) | 128GB/s (1Gbps per pin) | 256GB/s (2Gbps per pin) |

| tRC | 40ns(=1.5V) 48ns(=1.35V) | # | 48ns | 45ns |

| tCCD | 2ns (=4tCK) | 2ns (=4tCK) | 2ns (=1tCK) | 2ns (=1tCK) |

| VPP | Internal VPP | Internal VPP | External VPP | External VPP |

| VDD | 1.5V, 1.35V | 1.35V | 1.2V | 1.2V |

| Command Input | Single Command | Single Command | Dual Command | Dual Command |

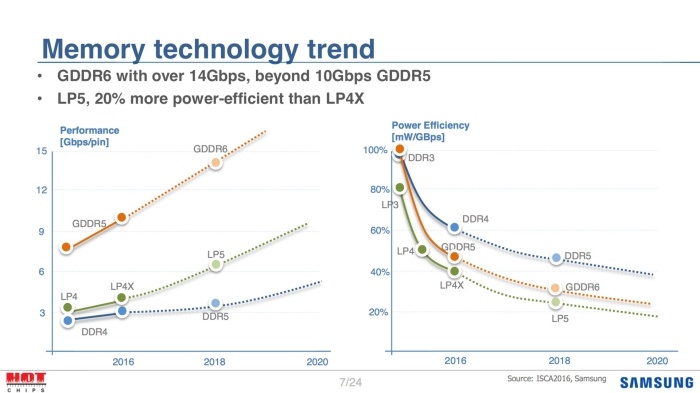

Messe momentaneamente da parte queste ultime, oggetto al momento di speculazioni di ogni tipo, è interessante notare come la tecnologia Synchronous Dynamic Random-Access Memory, che per quanto concerne le schede video avrebbe dovuto trovare il proprio capolinea con l'introduzione delle GDDR5X, sarà oggetto di un ulteriore upgrade con l'uscita delle GDDR6 grazie a Samsung mentre Micron, contrariamente alle attese, si occuperà forse solo di un leggero lifting delle prime (12 Gbps).

Previste per il 2018, le GDDR6 raggiungeranno una velocità di 16 Gbps con una tensione operativa invariata rispetto alle GDDR5X.