Ok,

Si, viene applicata la 'proprietà transitiva': DATA1 e CLK1 = waveform = DATA2 + CLK2, nei limiti di approsimazione del formato utilizzato (introducendo quindi errore), ma in che modo questo elimina i problemi di XRUN?

Non introduce nessun meccanismo di controllo di flusso, quindi dopo X tempo - esattamente come prima - il buffer andrà in underrun o overflow.

Non capisco.

Eccoci al punto, forse.

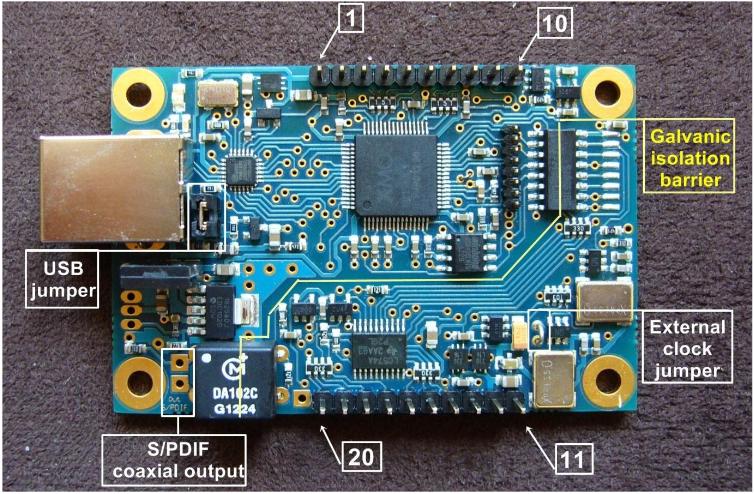

Nel DAC che ho io è presente un circuito di isolamento (un fifo ad 1 bit) e di reclock, che avviene sulla base del master clock ESTERNO. Immagino sia lo stesso anche nel tuo, il punto è che è un reclock SINCRONO rispetto al trasporto (la JLSOUND nel mio caso) che è il master, mentre il dac è lo slave.

Usando dac come il mio o il tuo a valle di qualcosa come TPA o IAN o ACKO (definiamolo 'accrocchio') si fanno 2 isolamenti e reclcocking in rapida successione, usando lo stesso clock, se si usa la BBB con TPA si rende 'sincrono' anche quel collegamento, scongiurando i problemi di XRUN.

Sia con l'interfaccia USB/I2s che con l'accrocchio, si raggiunge l'obiettivo di portare all'ingresso del DAC chip un segnale I2s sincrono rispetto ad un unico MCLK, 'ripulito' tramite l'isolatore e risincronizzato immediatamente a monte del dac.

Quello che non riesco a valutare è:

a. con l'accrocchio si hanno due isolamenti e reclocking in cascata, è utile, ininfluente o dannoso?

b. non sarebbe meglio - in termini assoluti - usare un clock posto nelle immediate vicinanze del dac chip rendendo il dac MASTER ed il trasporto (accrocchio e/o interfaccia) slave?

Comunque sia grazie, questa chiacchierata mi è stata molto utile per chiarirmi le idee.

Rispondi quotando

Rispondi quotando