1. SLC, MCL, TLC: quali le differenze?

Passando a fare una rapida carrellata sulle diverse tecnologie sviluppate nel tempo, prenderemo a spunto, d'ora in avanti, le temporizzazioni tipiche delle NAND Flash ottenute tramite processo produttivo dell'ordine dei "2xnm", dando modo di paragonare in maniera sintetica quanto accade nell'uso delle varie tipologia di memorie e, contemporaneamente, indicando anche i riferimenti sui tempi medi necessari alle complete attività di lettura, scrittura e cancellazione.

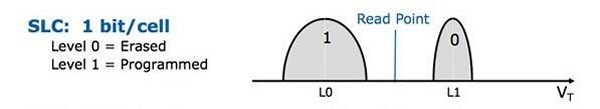

SLC

Le memorie NAND Flash SLC, le prime ad esser state utilizzate, adottano tipicamente una corrispondenza diretta tra la presenza/assenza di carica nel floating gate ed i valori binari "0" o "1", a livello logico assegnati.

In queste memorie, al momento in cui è necessario prelevare il contenuto della cella dovrà esser valutata l'esistenza, o meno, di una certa carica elettrica: l'operazione completa comporta in genere un tempo di lettura di ~25micro/s e la circostanza potrà condurre a determinare uno solo dei due valori digitali.

Figura 8: sistema funzionale a 1bit/2 livelli di tensione

Le operazioni di scrittura necessiteranno la generazione di un unico e ben definito livello di tensione e saranno eseguite in un tempo medio di ~250micro/s, mentre per quelle di cancellazione dei blocchi saranno necessari ben ~1.5milli/s.

Questo tipo di tecnologia a singolo bit, pur caratterizzandosi in eccellenti prestazioni ed in una invidiabile longevità operazionale, non consente d'altro canto di produrre unità allo stato solido di elevata capacità a prezzi comprensibilmente accettabili a livello SOHO.

Per questo motivo, un SSD che utilizza memorie NAND SLC ha la condizione essenziale di dover disporre di quantitativi davvero elevati di celle di memoria: tale circostanza, di conseguenza, diviene economicamente sconveniente relegandone l'uso in ambito Enterprise su server mission critical, potenti workstation professionali o appliance di storage di alto profilo, tutti estremamente costosi.

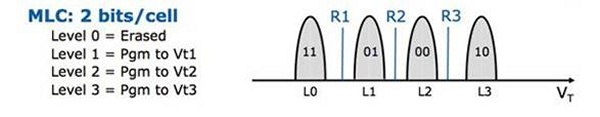

MLC

La prima evoluzione verso uno scenario maggiormente produttivo è stata quella dell'adozione di una più avanzata tecnologia in grado di mettere a disposizione una nuova generazione di celle polivalenti, congegnate alla base sull'idea di poter accettare differenti valori di carica o multilivello.

Questo nuovo tipo di transistor è pur sempre costruito a partire da dispositivi a semiconduttore identici ai precedenti, ma l'idea funzionalmente alla base è quella di rendere possibile, a livello logico, la memorizzazione al proprio interno di una quantità raddoppiata di informazioni.

Questa soluzione innovativa, la quale interessa fondamentalmente operazioni di scrittura e lettura più articolate, viene ottenuta riuscendo a gestire e controllare in maniera più precisa il livello di carica mantenendola entro ben definiti e distanziati livelli di tensione.

Si amplia, così, il concetto d'uso delle celle NAND tramite l'implementazione di una serie equidistante di valori di soglia da programmare nel floating gate: ad ognuno di questi valori (compreso lo stato di assenza di carica) è possibile associare a livello logico uno dei quattro valori digitali, "00" "01" "10" e "11", utilizzabili tramite due bit.

Figura 9: sistema funzionale a 2bit/4 livelli di tensione

Di pari passo a questa brillante soluzione si verificano, d'altro canto, una serie di circostanze penalizzanti a livello prestazionale.

Queste non sono solo inerenti il concreto aumento della velocità di esecuzione dei comandi in scrittura e lettura provenienti dal controller, ma vanno a produrre purtroppo anche una sensibile dilatazione dei tempi in fase di cancellazione, sebbene con tempi meno marcati in percentuale.

In fase di programmazione della cella queste latenze intervengono a causa dell'incremento del lasso di tempo necessario alla logica di controllo per determinare il corretto livello di tensione, tra i quattro possibili da poter applicare: livello che andrà poi a determinare, logicamente, la relativa coppia di bit.

Quest'attività porta il tempo di scrittura mediamente a quadruplicarsi rispetto all'equivalente scenario delle SLC, attestandosi sui ~900micro/s, mentre le operazioni di cancellazione dei blocchi di pagine salgono a ~3milli/s.

Sul fronte della lettura delle informazioni un'ulteriore sfida nell'uso delle celle multilivello è rappresentata, allo stato dell'attuale tecnologia di misurazione, dalla difficoltà di estrapolare in maniera diretta, con una singola verifica, il valore del livello di carica contenuto nella cella.

Tale circostanza operazionale costituisce di fatto una limitazione aggiuntiva che rende, in assoluto, meno performante anche la lettura: il tempo necessario va infatti a raddoppiare rispetto alle migliori NAND SLC, giungendo a temporizzazioni dell'ordine di ~50micro/s.

La soluzione comunemente adottata dai produttori per contenere al minimo questo gap temporale è quella dello sviluppo di una serie di complessi algoritmi in modo da facilitare l'estrapolazione del valore di carica elettrica.

Vengono sviluppate strategie di verifica sostanzialmente di tipo comparativo al fine di evitare di giungere all'overhead sistematico che tre o quattro rilevazioni comporterebbero ad ogni richiesta.

Queste strategie consistono, in sintesi, nell'assumere preventivamente un valore ben definito di tensione, prenderlo come riferimento e valutare, tramite una serie di veloci comparazioni sulla base di algoritmi specifici, la variazione del livello di carica dai singoli valori di soglia, permettendo di contenere le operazioni in genere a sole due verifiche.

Â

TLC

Le recenti TLC operano in maniera del tutto analoga alle MLC, con una modalità concettualmente ancora più efficiente e soprattutto economica, seppur stante ad un procedimento funzionale ancora più articolato.

A seguito dell'affinamento delle tecnologie produttive e le superiori caratteristiche delle più recenti celle di memoria NAND Flash, i produttori hanno pensato di ampliare il concetto alla base dell'idea multilivello, sviluppando una tecnologia in grado di impiegare otto distinte soglie di tensione.

In questo modo, potendo gestire l'uso di una corrispondenza digitale di otto bit, è possibile usufruire di altrettante permutazioni su base binaria e poter singolarmente memorizzare uno dei valori "000", "001", "010", "011", "100", "101", "110" o "111", con un evidente aumento dell'efficienza del dispositivo elettronico originario.

Figura 10: confronto tra i livelli funzionali delle varie tipologie di NAND

In misura del tutto analoga ai concetti espressi in precedenza per le MLC, il discorso diviene nelle TLC ancora più complesso, e penalizzante, al momento di attivare le operazioni di scrittura: alla luce del numero lievitato dei livelli di carica, deve esser gioco forza considerato un procedimento di maggior precisione ed affidabilità nella generazione del corretto valore di tensione (programmazione), il quale prevede ora un numero di soglie divenute anch'esse otto, utili a determinare a livello logico il contenuto, da tre bit, del dato da memorizzare.

Diventa pertanto inevitabile che le operazioni di scrittura sulle NAND TLC arrivino a risultare più lente in genere del 50% rispetto alle MLC, portando le temporizzazioni a salire a ~1300micro/s, mentre per la cancellazione dei blocchi sono necessari ~4.5milli/s.

Altro aspetto non secondario da tenere in considerazione è quello della diminuzione del delta di carica tra i distinti valori di tensione in gioco da attribuire alle nuovo numero complessivo di soglie.

La diminuita differenza di tensione tra i valori di soglia contigui, fa inoltre si che le operazioni di programmazione possano anche divenire soggette ad una serie ulteriore di disturbi del segnale all'insorgere delle correnti di leakage, soprattutto nei modelli che utilizzano chip con più ridotte geometrie costruttive: la coesistenza di queste circostanze determina, tendenzialmente, un numero maggiore di probabilità della rilevazione di errori nelle successive fasi di lettura.

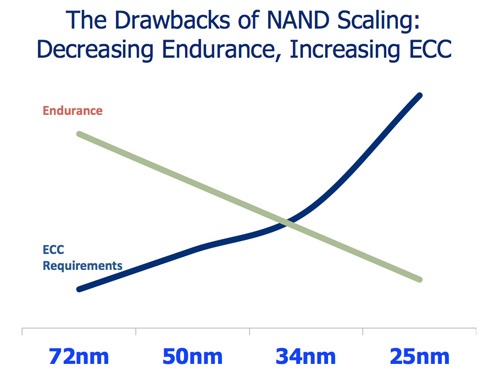

Figura 11: durata delle celle e quantità dei dati ECC sono inversamente proporzionali (fonte LSI)

Per la gestione di questo handicap si rende necessaria, di concerto, l'adozione di algoritmi di correzione di errore più complessi: questi, a loro volta, portano non solo all'esigenza di spazi di memorizzazione aggiuntivi ma, sostanzialmente, inducono al momento della loro elaborazione latenze aggiuntive nonché la necessità , nel controller, di una capacità di calcolo numerico più rilevante.

Così come già riferito per le Flash NAND MLC, bisogna in ultimo sottolineare che in fase di lettura non è possibile neanche nelle TLC verificare il valore di carica presente nel floating gate tramite rilevazione diretta.

Per mezzo di diverse strategie e mediante l'uso di specifici algoritmi si riesce, nelle migliori delle circostanze, a rendere in qualche modo più efficienti le operazioni di rilevazione del valore di tensione nel gate flottante, tramite una serie di misurazioni, in genere quattro, che portano la latenza in lettura a divenire sostanzialmente non inferiore ~75micro/s.