Introduzione

Per chi possiede un minimo di conoscenze di elettronica e di informatica, la prima grande differenza che intercorre tra le memorie Flash di tipo NAND più comunemente usate, SLC, MLC e TLC, risulterà intuibile direttamente dalla definizione dei relativi acronimi:

- SLC - Single Level Cell (1 bit per cella, 2 livelli di tensione)

- MLC - Multi Level Cell  (2 bit per cella, 4 livelli di tensione)

- TLC - Triple Level Cell  (3 bit per cella, 8 livelli di tensione)

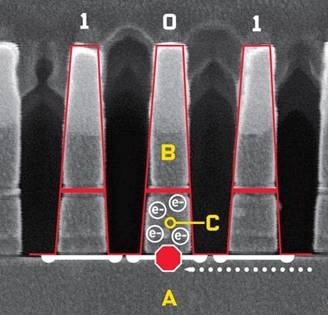

Figura 1: celle NAND 110.000x al microscopio elettronico (fonte Micron)

A (substrato) B (gate di controllo) C (gate flottante)

Una singola cella di memoria NAND Flash rappresenta di fatto l'unità elementare di memorizzazione nelle moderne unità di storage allo stato solido. E' costituita essenzialmente da un transistor relativamente particolare ad effetto di campo (FET) in tecnologia MOS (Metal Oxide Semiconductor), in quanto presenta la caratteristica di esser dotato di due terminali di attivazione (gate).

A partire dagli elementi costitutivi di un MOSFET è infatti previsto un secondo gate, di tipo flottante (floating gate), sottostante al gate di controllo (control gate): per questo motivo il transistor venne in origine definito FGMOS (Floating Gate MOS).

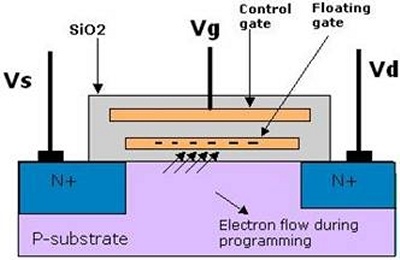

Figura 2: grafico di una tipica cella di memoria NAND Flash

Il terminale di attivazione aggiuntivo flottante viene usato per collegare le wordline al gate di controllo e costituisce uno spazio ben definito all'interno del transistor: ha capacità conduttive, è in genere di tipo poli-siliconico ed è in grado di trattenere della carica elettrica, riuscendo a mantenerla inalterata nel tempo.

Questa caratteristica riassume in sintesi la più essenziale delle proprietà delle memorie NAND Flash: la non-volatilità .

Il lasso di tempo per cui questa viene garantita, priva di apporto esterno di energia, va a definire il valore di Data Retention Period, in genere dell'ordine di uno o più anni: questo parametro è considerato, a detta dei più, fondamentale in quanto denoterebbe in qualche modo la qualità della tecnologia MOS utilizzata.

Figura 3: grafico della perdita media di efficienza con l'uso e il passare del tempo

Dal punto di vista dell'organizzazione a livello fisico, un die è tipicamente suddiviso in pagine da 4kB agglomerate in 1280 blocchi, in modo da formare un singolo insieme uniforme di 512MB: a livello di pagina, nelle memorie NAND Flash possono avvenire un numero illimitato di letture senza che questo fatto ne possa pregiudicare in alcun modo la durata.

Anche al momento della prima scrittura di una cella, sostanzialmente a drive giunto con impostazioni di fabbrica o a seguito di una procedura di secure erase, il procedimento di memorizzazione non comporta alcuna penalizzazione nella durata delle pagine interessate.

Per descrivere le implicazioni inerenti il procedimento finalizzato invece alla scrittura in esercizio, valevole per tutte le famiglie di memorie NAND, bisogna precisare che per una qualsiasi successiva riscrittura una cella deve essere prima di tutto bloccata e cancellata, o meglio in qualche modo svuotata della carica precedente (che, logicamente, rappresenta delle ben precise informazioni).

Questa operazione, definita tunnel erase, è attivata al momento che una tensione intermedia viene applicata al gate di controllo: l'energia applicata dà modo alla corrente di poter liberamente fluire, permettendo agli elettroni già presenti nel floating gate di esser rilasciati e svuotare, così, il gate flottante.

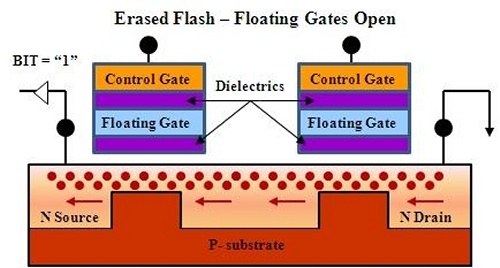

Figura 4: fase di cancellazione di una cella NAND

Successivamente la cella viene sbloccata ed è pronta per esser nuovamente utilizzata, ovvero riscritta tramite un procedimento di programmazione detto tunnel injection.

Esso consiste, qualora si volesse imporre il valore logico "0", binario, nell'applicazione di un potenziale di carica positiva tramite il quale una quantità di elettroni, di carica negativa, vengono trasferiti (iniettati) attraverso gli strati dielettrici del transistor, per esser infine trattenuti all'interno del floating gate.

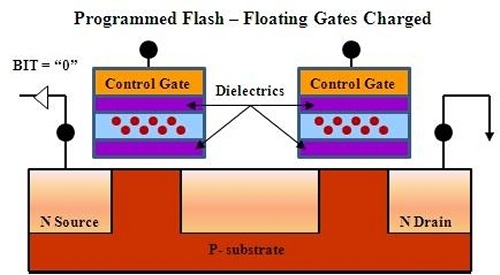

Figura 5: fase di programmazione di una cella NAND

L'altra alternativa possibile, quella di identificare cioè il valore "1", è circostanziata dalla non emissione di alcuna nuova carica, lasciando pertanto vuota di elettroni la cella in precedenza cancellata.

Per inciso, talvolta si può anche leggere in alcuni articoli o su pagine web che la corrispondenza tra gli stati e il valore di tensione viene descritta con modalità invertita, ovvero con lo "0" a significare uno stato privo di carica, ma è solo una descrizione a livello puramente teorico.

Bisogna, anche in questo caso, approfondire il fondamentale concetto di assenza di carica susseguente alle operazioni di cancellazione, puntualizzando quanto in realtà avviene: sebbene si parli comunemente del termine assenza, risulta in realtà molto complesso azzerare la tensione presente all'interno del floating gate.

La carica elettrica non può esser completamente eliminata, in quanto uno o più elettroni tendono in genere a rimanere naturalmente imprigionati all'interno dello strato di ossido, producendo così un seppur minimo livello di tensione.

Questo fatto non pregiudica le corrette funzionalità delle memorie NAND Flash in quanto tale carica permane ad un livello ben inferiore a quello del primo valore minimo di soglia, tale quindi da non divenire influente nelle successive rilevazioni durante le attività di lettura: almeno finché la cella continuerà a trovarsi, come vedremo, in stato di efficienza.

La sequenza di scritture, cancellazioni e successive riscritture, in continua alternanza sulle pagine costituite dalle celle, è detto nelle memorie NAND ciclo di program/erase.

Il valore accreditato dal produttore alle proprie celle di memoria è da considerare pertanto di vitale importanza ed utile quale criterio per stabilire e quantificare la durata del dispositivo di storage che le adotta.

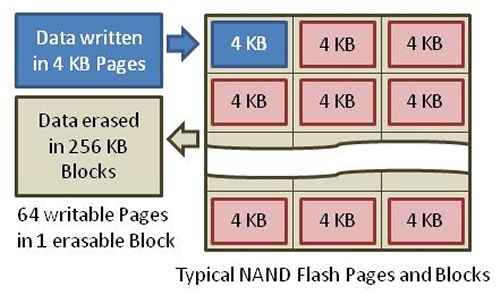

Figura 6: programmazione/cancellazione a pagine e blocchi di celle

Per denotare in qualche modo la complessità funzionale di queste memorie, bisogna chiarire che l'operazione di programmazione/cancellazione, seppur destinata in origine ad un'unica serie di celle/pagina, non può esser eseguita in modalità diretta solo su queste: è necessario infatti procedere alla preventiva cancellazione di un intero blocco cumulativo di pagine da 4kB contigue, in genere in numero di 64.

Stabilito che, spesso, all'interno del blocco di pagine interessato potrebbero esser già memorizzati altri dati non inerenti l'operazione in esecuzione, è facile intuire come questo fatto comporti spesso anche la necessità dello spostamento di una quantità di dati (256kB) non tutti sostanzialmente interessati alle operazioni originate del sistema operativo.

Il controller dell'unità SSD, che in queste circostanze attiva contestualmente le cosiddette strategie di wear leveling per salvaguardare la durata dell'unità nel tempo, procederà quindi nelle attività tramite due differenti operazioni: la prima, rappresentata dalla scelta di un nuovo blocco di pagine vuote di destinazione (cancellate già in precedenza) dove memorizzare i dati, la seconda comprendente sia la scrittura dei dati modificati nonché la riscrittura vera e propria (copia) del contenuto immutato del blocco appena cancellato.

Oltre al concreto handicap a livello di spazio di memorizzazione che non può, in questo modo, esser utilizzato nel lungo periodo in maniera del tutto efficiente, tutta questa serie di operazioni supplementari richiedono ovviamente anche un tempo ampiamente superiore all'ideale necessità di modifica dei dati originari.

All'esordio di questa tecnologia le prestazioni globali in scrittura rappresentavano, pertanto, un consistente limite, soprattutto nelle operazioni random, il tempo necessario alla copia tanto inevitabile quanto imprevista della serie di blocchi costituiva e costituisce ancora il fattore più limitante in assoluto, in quanto al crescere di questo intervallo vanno a diminuire in misura diretta le performance.

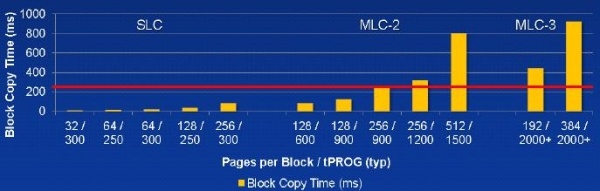

Figura 7: dilatazione delle temporizzazioni di copia dei blocchi in relazione all'innovazione tecnologica

Andando a riassumere sinteticamente le circostanze particolarmente negative di questa tecnologia, i fattori chiave che vanno ad impattare le performance in scrittura sono:

- l'elevato numero di pagine per blocco;

- l'aumentare del tempo necessario alla programmazione;

- la dilatazione delle temporizzazioni nei trasferimenti di I/O.

Questi limiti, uniti ad una iniziale non brillantezza nelle operazioni atomiche di scrittura delle NAND, furono in origine considerati fattori troppo penalizzanti nell'uso di questa tecnologia per pensare di poter soppiantare del tutto i dispositivi di storage, all'epoca più largamente utilizzati, a tecnologia meccanico-magnetica.