3. Architettura Sandy Bridge

Â

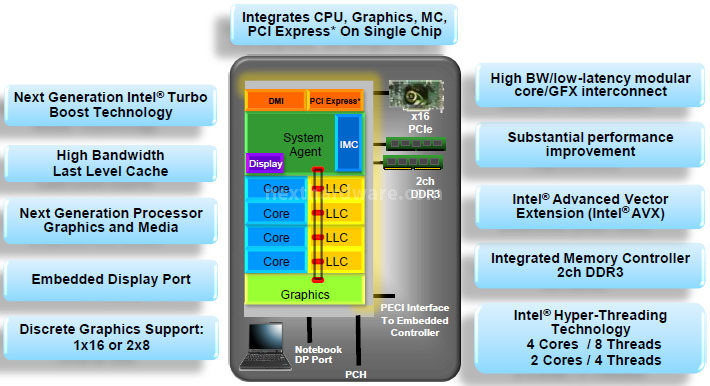

I processori Sandy Bridge integrano in uno solo chip sia la CPU che la GPU, abbandonando lâapproccio Multi Chip Package utilizzato fino ad oggi.

Â

Â

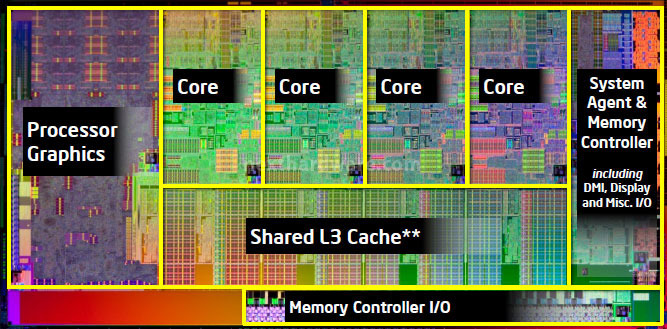

Allâinterno di ogni Sandy Bridge troviamo:

- 1 CPU dotata di 2 â 4 Core x86-64

- 1 Cache L3 condivisa tra CPU e GPU

- 1 GPU (con 6 o 12 Unità di elaborazione)

- 1 System Agent con controller della Memoria DDR3 e 16 linee PCI-E 2.0

Â

System Agent

Â

Il System Agent ricopre tutte le funzionalità che erano in passato integrate nel north bridge e che nelle CPU Nehalem è identificabile come Uncore. A differenza di questâultimo, però, la frequenza operativa non può essere gestita in modo indipendente da quella della CPU.

Il controller di memoria integrato è di tipo DDR3 Dual Channel con supporto ufficiale a moduli con frequenza di 1333 MHz. Per le CPU i7 e i5 è possibile impostare divisori della memoria differenti, alzando la frequenza delle stesse sino a 2133 MHz senza innalzare il BUS.

Â

Â

La CPU mette a disposizione 16 linee PCI-E 2.0 per il collegamento di una GPU discreta, eventualmente allocabili in due canali da 8 linee ciascuna per il supporto di configurazioni AMD CrossFireX o NVIDIA SLI. A causa del ridotto numero di linee PCI-E, molti produttori di schede madri hanno deciso di integrare bridge PCI-E al fine di aumentare il numero massimo di linee utilizzabili dai vari controller integrati (PLX, NVIDIA NF200, etc.).

Attraverso il BUS DMI, il System Agent collega la CPU al PCH (Platform Controller HUB). Questo BUS è caratterizzato da un ampiezza di banda pari a 20 Gb/s suddiviso in 4 canali da 64 bit a 5 Gb/s ed è il principale collo di bottiglia per la piattaforma Sandy Bridge, basti pensare che ogni porta SATA di ultima generazione può occupare fino a 6 Gb/s di banda e che ogni controller USB 3.0 occupa 5 Gb/s.

Â

Cache L3

Â

La cache di terzo livello è condivisa tra tutti i componenti del processore ed è collegata a questi con un Ring BUS. Non è presente un gestore centralizzato come in Nehalem, migliorando di fatto la scalabilità di questa soluzione al crescere del numero dei core. Ogni componente ha un accesso dedicato sul BUS e può accedere a tutti i dati presenti nella cache L3. La GPU può utilizzare la cache L3 per le sue operazioni, ma il quantitativo massimo allocabile è fissato a priori e varia a seconda del modello di processore; i core, invece, non hanno invece alcun limite di questo tipo. Su alcune schede madri è possibile variare la quantità di cache L3 allocabile per la GPU, ma questa operazione sembra causare instabilità o mancato avvio della macchina.

Â

Â